40GE 100GE TAP Aggregator TAP Switch

VPP Traffic Visualization Processor Network Packet Broker / Network TAP Switch

Non-modular flow traction protector

NT-iMXTAP-24G-E Technical White Paper

NT-VPP-5600 series Technical White Paper

NT-FTAP-32QCX Technical White Paper

NT-CFTAP-28XG-D Technical White Paper

Visual control based on the whole life cycle of bypass traffic data

The Solution of "Micro-burst" in SAPN traffic Collection Scenario

It should be responsive and delivered quickly to meet emergency needs

Traffic data deduplication & Path Analysis - the perfect solution

Traffic data Management - NSLP 2.

Backtracking analysis is perfectly applied to NSLP 2.0

The Evolution of traffic data management requirements

Cloud computing network traffic data management

Application of "Packet deduplication" in "Network Visualization Analysis"

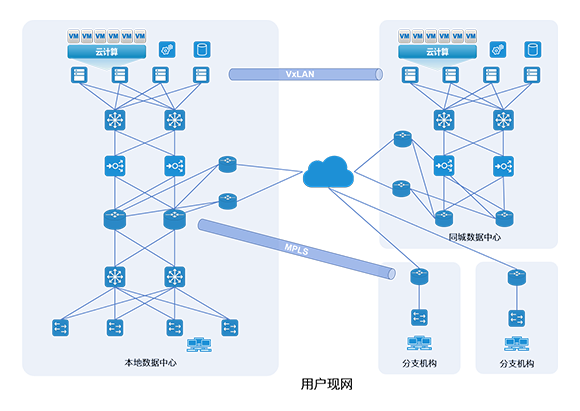

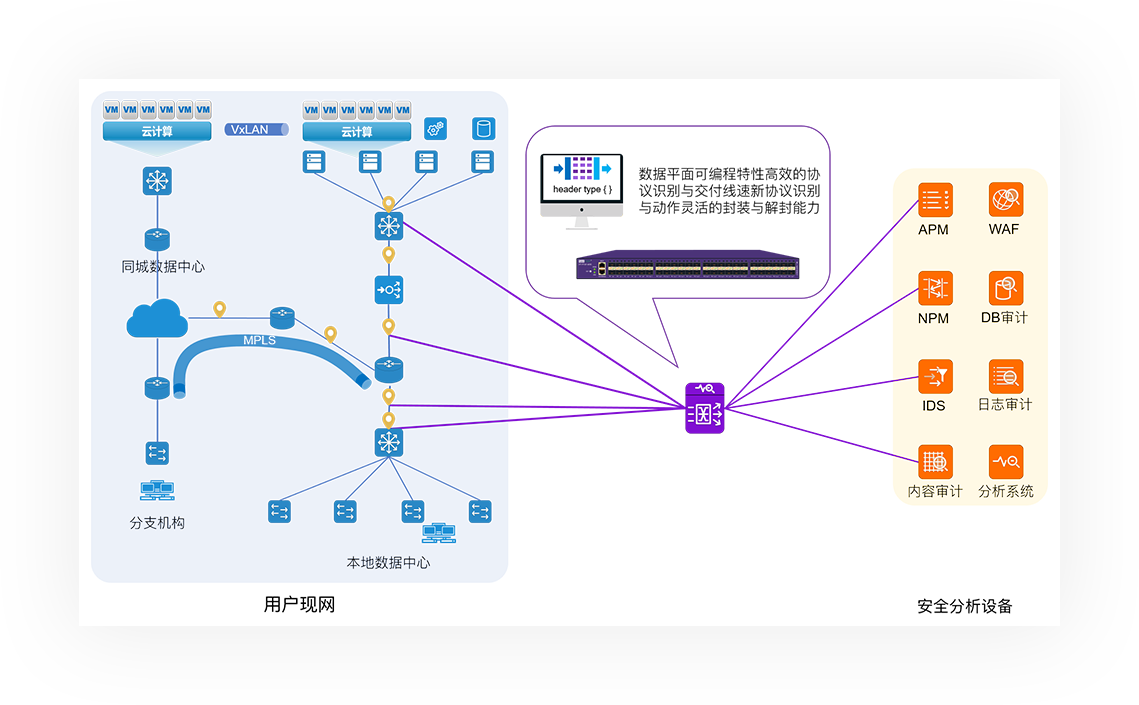

With the growth of user business, the IT architecture will design more new technologies, especially the introduction of cloud computing, the user's overall network will be more agile and open; High bandwidth, high reliability, and business diversity have become the norm of IT.

Traffic data control is an important part to ensure the robustness and security of IT network. How to support new network technologies and achieve rapid delivery of new application scenarios in traffic data applications has become a challenge for IT managers.

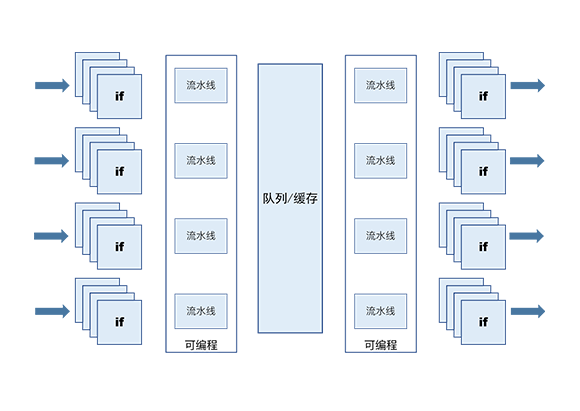

The powerful performance comes from the programmable chip. The system adopts the programmable traffic processor architecture, which can flexibly deal with the more agile and changing business environment, and has the ability to tell the new protocol adaptation and DPI operation.

Support more new business scenarios

With the upgrade of user service network, there are more new service scenarios, such as VxLAN, MPLS, heterogeneous encapsulation nesting, 3-layer VLAN nesting, appending hardware level timestamp, etc. It is difficult for traditional traffic control devices to realize such requirements because they cannot recognize the new protocol encapsulation. Programmable processors can more easily meet such challenges through programmable design of data plane

Wire-speed DPI packet processing

Programmable chip based on hardware packet processing engine, can achieve deep packet inspection level protocol identification and action, effectively eliminate the network bottleneck

Longer service lifetime

With the change of IT driven by business, network architecture or network technology needs to adapt to new business changes. Programmable processor is easier to support new protocol types and can provide longer service life cycle

DPI application layer identification

Packet slicing

Packet distribution

MAC address replacement

Tuple filtering

Timestamp marking

Packet marking

Custom offset matching

Packet masking

Packet deduplication

Replication and aggregation

Send and receive multiplexing

联系我们

联系我们